August 16, 2024

The down-scaling of gate length in silicon-based transistors results in an extremely low on-state drain-source resistance, presenting a challenge for test engineers to achieve precise and repeatable wafer measurements.

August 16, 2024

The down-scaling of gate length in silicon-based transistors results in an extremely low on-state drain-source resistance, presenting a challenge for test engineers to achieve precise and repeatable wafer measurements.

A new webinar is now open for registration – Making Accurate and Consistent Wafer Measurements with Next Generation Guarded True-Kelvin MEMS DC Probes.

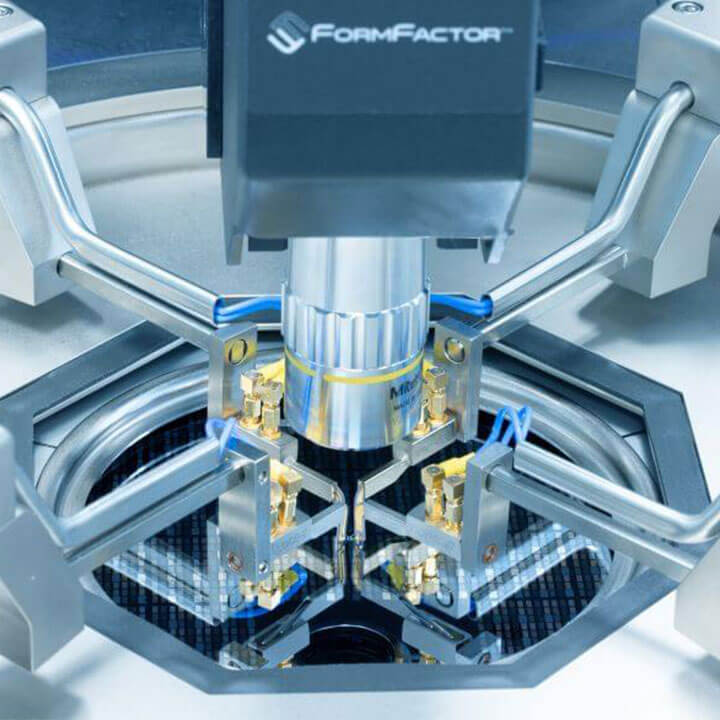

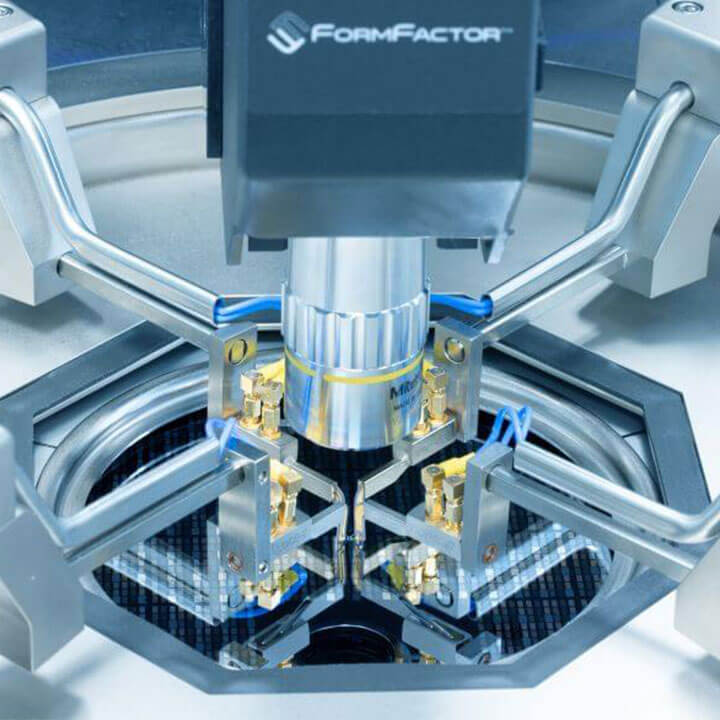

The down-scaling of gate length in silicon-based transistors results in an extremely low on-state drain-source resistance, presenting a challenge for test engineers to achieve precise and repeatable wafer measurements. Additionally, the reduction in size of aluminum-capped copper test pads to cut lithography, prototyping, and production costs complicates re-probing the same device with low contact resistance. This work proposes the use of novel true-Kelvin MEMS analytical DC probes, along with new test and modeling strategies, to address these emerging testing challenges.

Dr. Choon Beng Sia, Technical Director, Applications Engineering will be leading this webinar. Dr Choon Beng Sia is a SSG Fellow, conferred by the President of the Republic of Singapore. At FormFactor’s Center of Expertise, he is a Technical Director responsible for developing solutions to overcome semiconductor wafer test challenges. Dr Sia serves in the IEEE MTT-3 technical committee, defining standards and best practices for RF measurements. He is also a lecturer of the MTT-3 speaker bureau, specialising in wafer RF and 5G tests. Dr Sia is a recipient of multiple best paper awards at international conferences, publishing more than 50 scientific papers, holding 13 international patents.